作为IC的设计和验证人员,主要的工作都是在tapeout之前。那tapeout之后工厂生产出来的芯片是直接交到客户手上吗?

显然不行,生产出来的芯片还需要通过各种测试和筛选,保证客户拿到手里就是能用的。这项工作就是由测试工程师完成的。

其实测试工程师的工作并不一定开始于tapeout后,有时候甚至是跟IC设计是同步的。如果是一颗比较新的芯片,测试工程师要花时间去熟悉它的功能,还要准备测试的项目和程序代码。如果是一颗比较成熟的芯片,有现成的资源可以利用,开始的时间就可以晚一点。

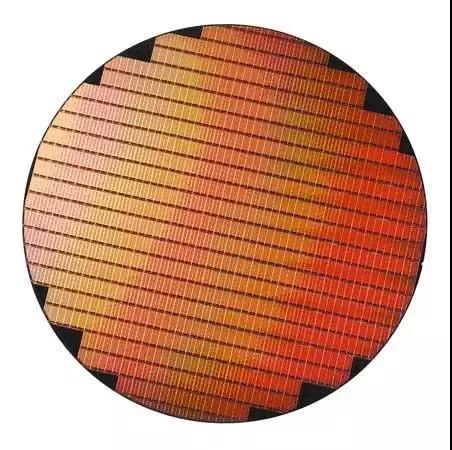

设计最终的版图交付于工厂流片(tapeout)后,大概过几个月的时间,工厂就会让你去拿wafer。wafer就像一个圆形的作业本,上面的一个个格子就是我们的单颗芯片:

我们先进行wafer level的测试,主要是一些基本功能的测试。比如上电power on、基本的用户功能、测试功能等等。

接下来就是后续的Package level的测试以及量产测试了,首先一上来就是开短路测试,把一些接触好的芯片先刷出来。既然是量产测试,open-short测试fail的不一定是芯片本身的问题,还有可能是测试机台的问题。因此量产测试会进行很多次,这样通过每次的良率和最终的良率可以确定是芯片本身的问题还是测试机台的问题,因为每一遍都会重新更换芯片在测试机中的位置。

然后开始测试一些具体的功能,这个由于各个芯片的功能不一样,所以不详细展开了。在测试过程中还要对特定的parameter进行trim,毕竟waferlevel和package level 用到的parameter值并不一定是一样的,而且不同产品之间也是不同的。

在测试过程中会涉及到很多测试项目(测项),需要在测试程序中定义好每个测项的softbin和hardbin,这样测试完成后,就可以清楚的知道是哪些fail,方便分析。

鸿怡电子提供供量产测试中所用到的FT测试座,针对不同封装芯片的量产测试座,测试治具。为IC测试工程师在作后期的芯片量产测试时提供了很大的便利!!